在北京理工大學(xué)《集成電路設(shè)計(jì)實(shí)踐一》這門重要的專業(yè)實(shí)踐課程中,VHDL(VHSIC Hardware Description Language,超高速集成電路硬件描述語言)的掌握是連接理論知識與實(shí)際硬件設(shè)計(jì)的核心橋梁。它不僅是描述數(shù)字系統(tǒng)行為的軟件工具,更是實(shí)現(xiàn)從概念到芯片的關(guān)鍵開發(fā)手段。

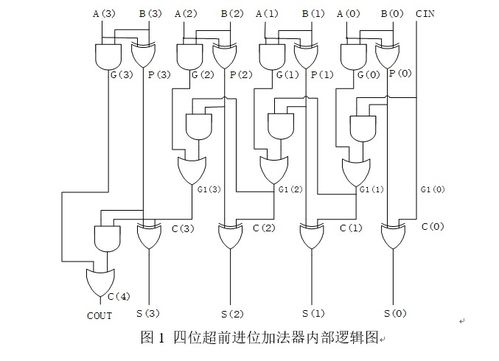

VHDL作為一種強(qiáng)大的硬件描述語言,在課程中扮演著多重角色。它允許學(xué)生使用高級的、類似于軟件編程的語法,來精確描述復(fù)雜的數(shù)字邏輯電路,如寄存器、狀態(tài)機(jī)、算術(shù)邏輯單元等。與直接繪制電路圖相比,VHDL提供了更高的抽象層次和靈活性,便于進(jìn)行大規(guī)模、模塊化的設(shè)計(jì)。在“軟件開發(fā)”的語境下,這里的“軟件”特指用于描述、模擬和綜合硬件電路的代碼與開發(fā)環(huán)境。學(xué)生通過編寫VHDL代碼,實(shí)質(zhì)上是在進(jìn)行一種特殊的軟件開發(fā)——其最終產(chǎn)物是硬件電路的結(jié)構(gòu)或行為。

課程實(shí)踐通常圍繞典型的數(shù)字系統(tǒng)設(shè)計(jì)流程展開:

- 設(shè)計(jì)輸入:學(xué)生使用集成開發(fā)環(huán)境(如Intel Quartus Prime、Xilinx ISE/Vivado),將電路構(gòu)思轉(zhuǎn)化為結(jié)構(gòu)清晰、符合規(guī)范的VHDL代碼。這要求熟練掌握VHDL的基本結(jié)構(gòu)(實(shí)體、結(jié)構(gòu)體)、數(shù)據(jù)類型、并行語句和順序語句。

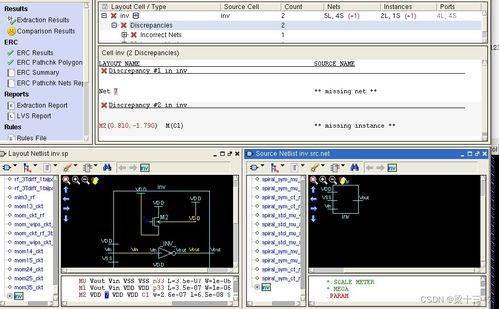

- 功能仿真:編寫測試平臺(Testbench),對設(shè)計(jì)模塊施加激勵信號,通過軟件仿真驗(yàn)證其邏輯功能的正確性。這個階段完全在軟件環(huán)境中進(jìn)行,是排查邏輯錯誤的關(guān)鍵,深刻體現(xiàn)了“軟件開發(fā)”中的調(diào)試與驗(yàn)證思想。

- 綜合與實(shí)現(xiàn):利用綜合工具,將行為級的VHDL描述“編譯”和優(yōu)化成目標(biāo)工藝(如FPGA)對應(yīng)的門級網(wǎng)表。這個過程將抽象的代碼映射為具體的硬件資源,是硬件設(shè)計(jì)軟件化的核心體現(xiàn)。

- 時序分析與下載測試:對綜合后的設(shè)計(jì)進(jìn)行時序分析,確保滿足時鐘頻率要求,最終將生成的配置文件下載到FPGA開發(fā)板進(jìn)行實(shí)物驗(yàn)證。

要成功掌握本課程中的VHDL軟件開發(fā),學(xué)生需注重以下幾點(diǎn):

- 理解硬件思維:牢記VHDL描述的是并行執(zhí)行的硬件電路,這與傳統(tǒng)串行執(zhí)行的軟件編程有本質(zhì)區(qū)別。清晰的硬件結(jié)構(gòu)觀念是寫出高效、可綜合代碼的基礎(chǔ)。

- 熟練核心語法與設(shè)計(jì)模式:深入理解進(jìn)程、信號與變量的區(qū)別,掌握有限狀態(tài)機(jī)、數(shù)據(jù)路徑等經(jīng)典結(jié)構(gòu)的VHDL實(shí)現(xiàn)方法。

- 善用開發(fā)工具:熟悉IDE的工程管理、仿真調(diào)試、綜合約束等各項(xiàng)功能,能高效利用工具定位和解決問題。

- 實(shí)踐驅(qū)動學(xué)習(xí):通過完成課程中從簡單組合電路到復(fù)雜數(shù)字系統(tǒng)(如小型CPU、通信接口)的一系列設(shè)計(jì)項(xiàng)目,在實(shí)踐中鞏固和深化對VHDL語言的理解與應(yīng)用能力。

在北京理工大學(xué)《集成電路設(shè)計(jì)實(shí)踐一》中,VHDL語言的掌握絕非簡單的編程學(xué)習(xí),而是培養(yǎng)硬件系統(tǒng)級設(shè)計(jì)能力、貫通“軟硬件界面”的核心實(shí)踐。熟練運(yùn)用VHDL進(jìn)行“軟件開發(fā)”,是學(xué)生邁向?qū)I(yè)集成電路設(shè)計(jì)工程師道路上的堅(jiān)實(shí)一步。