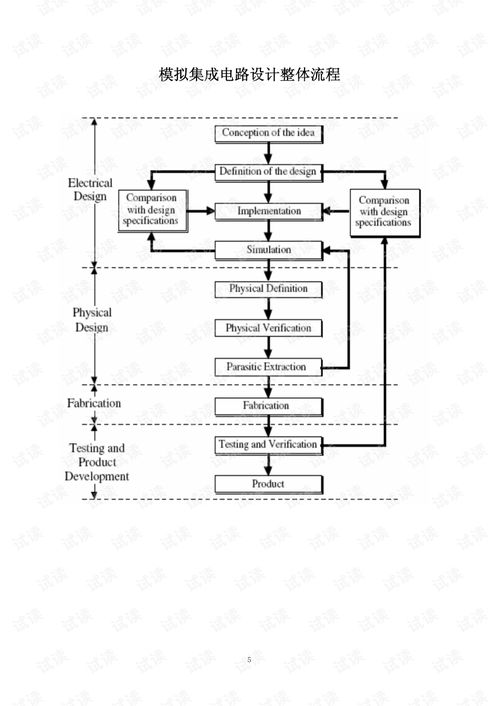

為滿足現代集成電路設計教學與科研的迫切需求,開發一套功能完善、操作便捷的《模擬CMOS集成電路設計實驗指導》配套軟件,已成為提升教學質量與效率的關鍵環節。本方案旨在構建一個集理論學習、電路仿真、實驗指導與結果分析于一體的綜合平臺。

一、 軟件開發目標與定位

軟件的核心目標是成為《模擬CMOS集成電路設計》課程的“虛擬實驗室”。它不僅應提供詳盡的實驗步驟與原理說明,更應深度融合行業標準EDA工具(如Cadence Virtuoso、Synopsys HSPICE等)或集成高性能開源仿真引擎,使用戶能夠在軟件引導下,完成從電路設計、參數設置、仿真分析到性能優化的完整流程。其定位是輔助教學,降低實驗環境搭建的硬件門檻,同時為學生提供可重復、可探究的自主實踐空間。

二、 核心功能模塊設計

- 實驗管理模塊:軟件以課程經典實驗為主線,如單級放大器、差分對、電流鏡、運算放大器、振蕩器等。每個實驗單元包含:

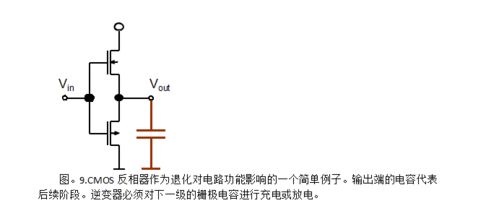

- 實驗原理:交互式圖文與動畫講解MOS管工作原理、電路拓撲及關鍵公式。

- 設計指標:明確給出增益、帶寬、功耗、擺幅等待優化目標。

- 步驟引導:提供分步操作指引,從創建電路圖、設置器件模型參數到配置仿真類型。

- 參考電路:提供可查看、可加載的基礎電路模板。

- 電路設計與仿真集成模塊:這是軟件的核心。

- 原理圖編輯器:集成一個簡化的圖形化電路繪制界面,支持基本CMOS器件、信號源、負載的拖拽放置與連線。

- 仿真引擎接口/集成:可調用外部EDA工具進行仿真,或在軟件內集成輕量級SPICE仿真內核。用戶能直接配置DC、AC、瞬態、噪聲等分析。

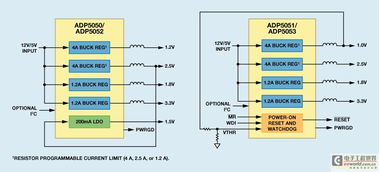

- 模型庫管理:集成常見工藝角(TT, SS, FF等)的晶體管模型文件,方便用戶選用。

- 數據可視化與分析模塊:

- 波形查看器:實時繪制并顯示仿真輸出的電壓、電流波形,支持多窗口對比、坐標縮放、測量光標等功能。

- 自動測量與報告:能根據設計指標,自動從仿真結果中提取增益、-3dB帶寬、相位裕度、功耗等參數,并生成格式化實驗報告草稿。

- 性能分析:提供基本的數據處理工具,如FFT分析、參數掃描結果繪圖等。

- 知識庫與幫助系統:

- 器件手冊:集成MOSFET的詳細特性與模型參數說明。

- 常見問題解答:針對實驗過程中可能遇到的仿真不收斂、結果異常等問題提供排查指南。

- 視頻教程:關鍵操作節點的短視頻演示。

三、 技術實現路徑

- 架構選擇:建議采用客戶端-服務器架構。客戶端提供用戶交互界面,服務器端處理仿真計算任務(尤其是集成仿真引擎時),以支持分布式計算并管理許可證。也可采用功能豐富的桌面應用程序形式。

- 開發工具與框架:客戶端界面可采用Qt(C++)或Electron(JavaScript/HTML5)框架開發,以實現跨平臺兼容性。服務器端可選用Python或C++,利用其豐富的科學計算庫(如NumPy, SciPy)進行數據處理和仿真后端開發。

- 仿真集成策略:優先考慮與成熟EDA工具的命令行接口集成,通過腳本自動化控制仿真流程。長期可考慮集成開源SPICE仿真器(如ngspice、XYCE)作為內置選項,以增強軟件獨立性。

- 數據與交互:使用SQLite或輕量級數據庫管理用戶項目、實驗數據和配置信息。確保軟件各模塊間數據傳輸流暢,狀態同步。

四、 教學應用與優勢

該軟件將傳統紙質實驗指導書轉化為動態、交互的數字體驗。其優勢在于:

- 降低入門門檻:學生無需在初期復雜配置專業EDA環境,可專注于電路原理與設計方法本身。

- 提升實驗效率:標準化的操作流程和自動化的報告生成,節省了大量重復性操作時間。

- 支持探索性學習:學生可輕松修改電路參數、更換拓撲,即時觀察性能變化,深化對理論的理解。

- 教學管理便利:教師可分發實驗模板,統一評估標準,并通過軟件收集學生實驗結果。

五、 挑戰與展望

開發過程中的主要挑戰包括:仿真精度與商用工具的可比性、復雜電路仿真的計算效率、以及軟件與日新月異的工藝模型的同步更新。軟件可向云端化、協作化方向發展,支持多人遠程實驗,并引入人工智能輔助,實現電路結構的初步推薦與優化建議,使之成為模擬IC設計人才培養的更智能伴侶。

開發《模擬CMOS集成電路設計實驗指導》軟件,是一項融合了集成電路知識、軟件工程與教育技術的系統工程。它的成功實施,將有力推動相關課程的教學改革,為學生構建從理論到實踐的無縫橋梁。