在當今信息技術飛速發展的時代,半導體集成電路(IC)作為電子設備的核心,其性能與可靠性直接決定了最終產品的成敗。炬豐科技深諳此道,將半導體工藝、可靠性設計與軟件開發三者深度融合,構建了一套從晶圓到系統的全鏈路質量與創新保障體系。

一、半導體工藝:可靠性的基石

半導體工藝是集成電路制造的物理基礎。炬豐科技專注于先進制程的研發與應用,從材料選擇、光刻、刻蝕、摻雜到薄膜沉積,每一個環節都精益求精。通過引入人工智能與機器學習算法對工藝參數進行建模與優化,公司能夠精確控制關鍵尺寸、減少缺陷密度,從而在源頭上提升芯片的固有可靠性。例如,在開發用于汽車電子或工業控制的高可靠性芯片時,工藝團隊會特別關注器件的抗輻射能力、溫度穩定性及長期電遷移效應,確保芯片能在嚴苛環境下穩定工作數十年。

二、集成電路的可靠性設計:超越功能實現

可靠性設計是連接工藝與最終應用的橋梁。炬豐科技的設計理念是“可靠性內建”(Reliability by Design),而非事后補救。這包括:

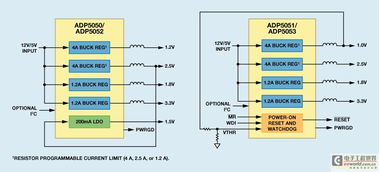

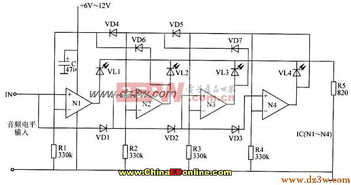

- 電路級設計:采用冗余設計、糾錯編碼(ECC)、片上監控電路(如溫度傳感器、電壓探測器)等技術,使芯片具備自我檢測與容錯能力。

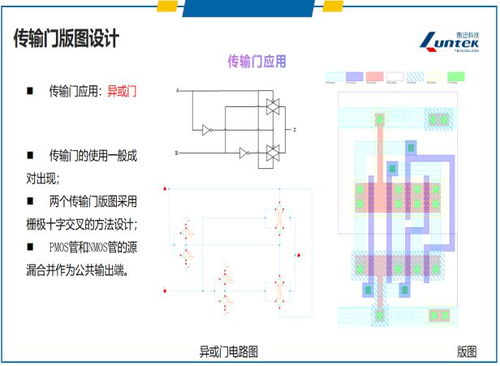

- 版圖與物理設計:通過電遷移(EM)和靜電放電(ESD)的仿真分析,優化電源網絡和I/O布局,避免因電流密度過高或瞬時電壓沖擊導致的失效。

- 老化與壽命預測:利用可靠性模型(如Black、Coffin-Manson模型)和加速壽命測試(ALT)數據,在設計階段就預測產品在預期壽命內的失效率,指導設計裕量的設定。

三、軟件開發:賦能全流程的智能引擎

在炬豐科技的實踐中,軟件開發已滲透到半導體價值鏈的每一個環節,成為提升工藝水平和設計可靠性的核心驅動力。

- 工藝開發與制程控制軟件:公司開發了專用的工藝仿真平臺和實時監控系統。這些軟件能夠對復雜的物理化學反應進行多尺度模擬,預測工藝結果,并利用大數據分析從生產設備中收集的數據,實現工藝窗口的實時優化與偏差的快速糾正,顯著提升了工藝的一致性與成品率。

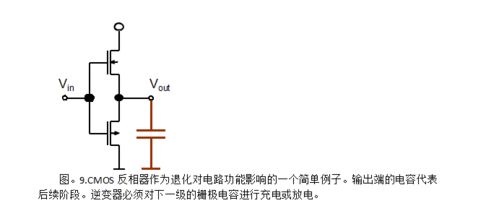

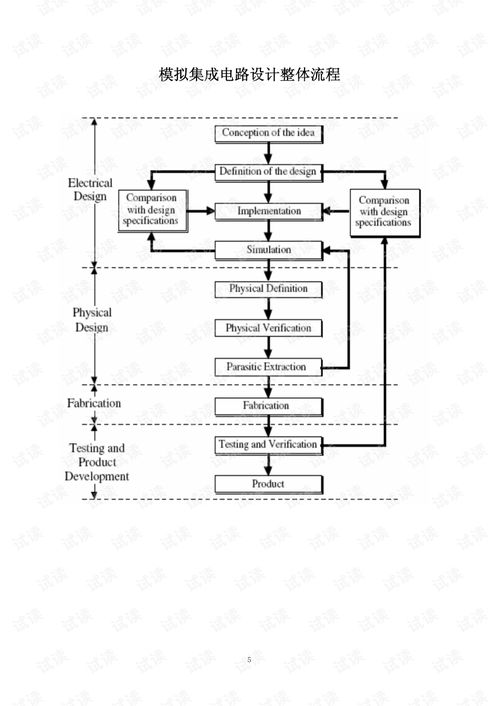

- 電子設計自動化(EDA)工具與內部套件:除了使用業界主流EDA工具進行前端設計和后端實現外,炬豐科技還自主研發了多項輔助軟件。這些工具專注于可靠性分析,例如,自動進行信號完整性(SI)/電源完整性(PI)分析、熱分布模擬、以及針對特定失效機制(如負偏壓溫度不穩定性NBTI)的退化仿真。它們與設計流程無縫集成,使設計師能在設計早期就識別并消除可靠性風險點。

- 可靠性測試與數據分析平臺:軟件開發團隊構建了統一的測試管理、數據采集與分析平臺。該平臺能自動化處理海量的可靠性測試數據(如HTOL高溫工作壽命測試、ESD測試等),運用統計分析和機器學習算法,快速定位失效模式,追溯根本原因,并生成詳細的可靠性報告。這不僅加快了產品認證速度,還為工藝和設計的迭代改進提供了精準的數據反饋。

- 面向應用的系統級健康管理軟件:對于最終的客戶系統,炬豐科技提供配套的軟件棧,用于監控芯片在實地運行中的健康狀況。這些軟件可以讀取芯片內置傳感器的數據,評估性能衰減,甚至預測潛在故障,實現預防性維護,從而將芯片的可靠性價值延伸到整個產品生命周期。

四、融合創新與未來展望

炬豐科技認識到,半導體工藝、可靠性設計與軟件開發三者并非孤立的環節,而是一個緊密耦合的循環。先進的工藝為高性能、高可靠設計提供了可能;嚴謹的可靠性設計思想指導著工藝和軟件的開發方向;而強大的軟件工具則使前兩者的復雜分析與優化成為現實,并不斷產生新的洞察。

隨著物聯網、人工智能、5G和汽車電子等領域的深入發展,對半導體集成電路的可靠性要求將愈發嚴苛。炬豐科技將繼續加大在軟件算法、仿真模型和智能分析平臺上的投入,推動工藝-設計-軟件的協同創新,致力于為客戶提供從芯片到系統、從設計到運維的全方位高可靠性解決方案,在激烈的全球半導體競爭中構建堅實的技術壁壘。